平ラグは15P(アンプ部)・4P(+B電源)・10P(+B1電源他)を予定していた。ところがアンプ部の15Pには到底パーツが乗り切らないことが判明した。

回路構成がほぼ同じ6T9 CSPPアンプでは12P×2個となっている。24Pが15Pに減って9P分が立ラグに乗るかといったら無理だ。そこで1L2Pの立ラグを1L3Pの立ラグ小に変更し、シャーシ内に6Pの平ラグを1個追加することにした。

OPTの配線穴のところには追加した6Pの平ラグを置き、真空管ソケット下には1L3Pの立ラグ小を配置する。

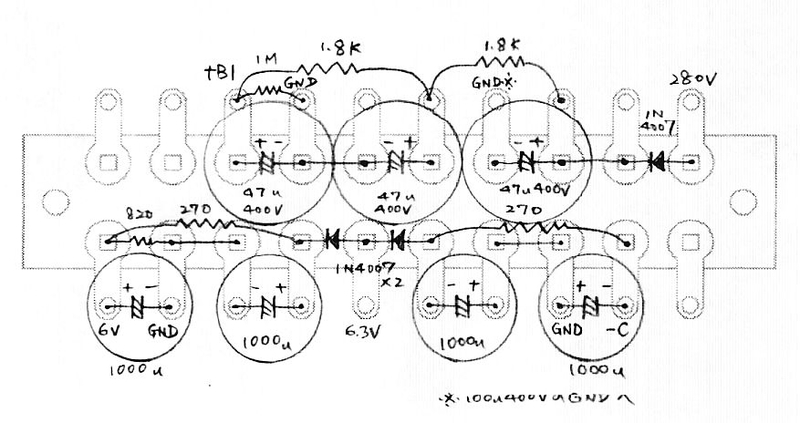

+B電源基板。パターンが気に入らないが4Pに収まっている。

+B1電源・6V系・-C電源基板。10Pを予定していたがラグが余った。

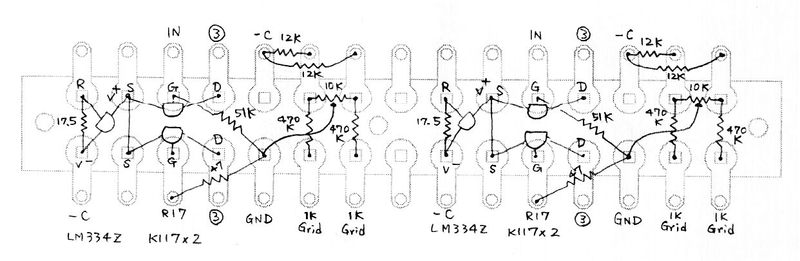

アンプ部基板。2SK117の発振防止ゲート直列抵抗はFETの足に直付けする。真ん中が1P分余っている。

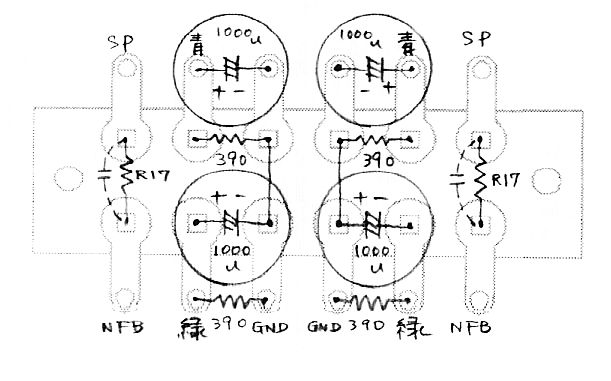

追加した6Pの平ラグにはカソードのコンデンサと抵抗、NFB抵抗を取り付ける。

当初の見積もりが甘かったが、無い頭をひねって考えたらこんなふうになった。